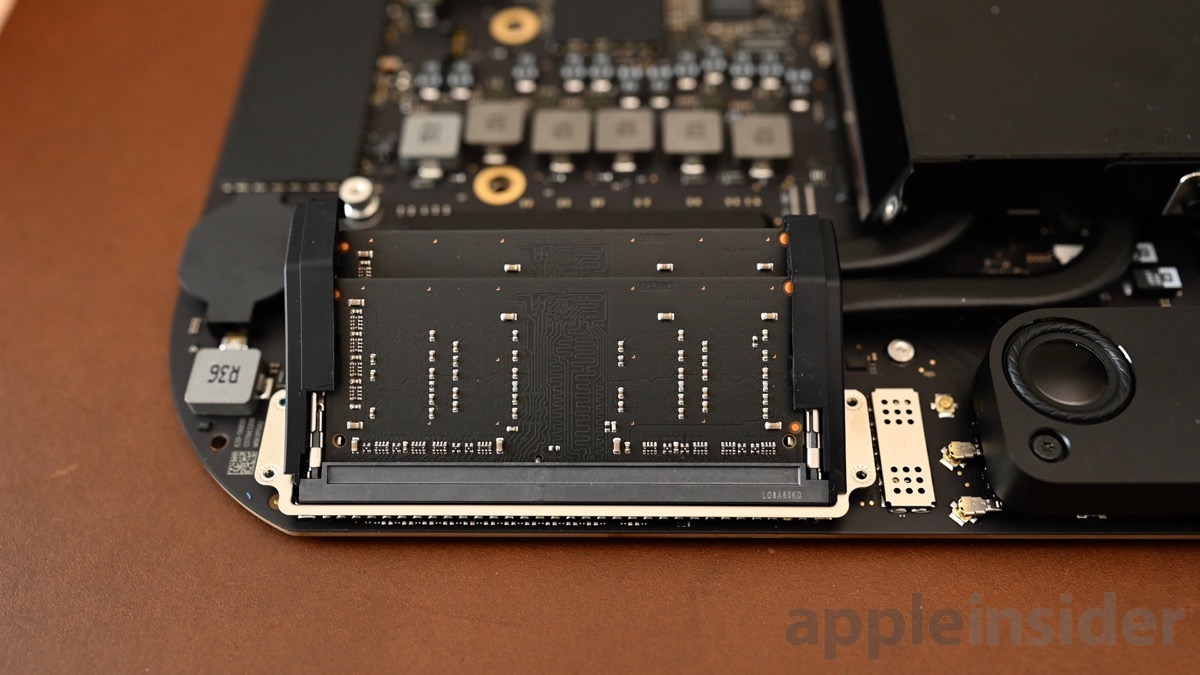

New DDR5 SDRAM standard supports double the bandwidth of DDR4

JEDEC, the controlling body of the RAM standard, has published details about the DDR5 SDRAM spec to address the demand for ever-faster RAM.

The new DDR5 spec is designed to enable scaling memory performance without degrading channel efficiency at higher speeds. This was done by doubling the burst-length to BL16 and bank-count to 32 from 16. DDR5 DIMM also has two 40-bit independent sub-channels, increasing efficiency, and reliability.

A new feature deemed Decision Feedback Equalization (DFE) enables IO speed scalability for higher bandwidth and performance improvement. DDR5 supports double the bandwidth of its predecessor, DDR4 with 4.8 gigabits per second possible — but not shipping at launch.

DDR5 also supports on-die ECC scaling features, which enable manufacturing on advanced process nodes.

"The DDR5 standard offers the industry a critical advancement in main memory performance to enable the next-generation of computing required to turn data into insight across cloud, enterprise, networking, high-performance computing and artificial intelligence applications," said Frank Ross, JEDEC Board of Directors member and senior member of Technical Staff at Micron.

Power requirements were dropped from 1.2V to 1.1V compared to DDR4. A voltage regulator on DIMM design reduces power consumption and offers better voltage tolerance for better DRAM yields. DDR5 uses the MIPI Alliance I3C Basic specification for system management bus.

"DDR5 is prepared to improve the Computing Performance by applying various features to overcome future technology scaling challenge and improve performance compared to DDR4. On this basis, DDR5 will lead the evolution of the data-centric era, and will play a pivotal role in the 4th Industrial Revolution," said Uksong Kang, Head of DRAM Product Planning at SK hynix, one of the JEDEC members. "SK hynix is opening up a new sector in the market through the development of the industry's first DDR5 that meets JEDEC standards. We have been working with many partners to verify DDR5 Ecosystem through development of test chips, and modules since 2018, and doing our best to secure mass-production levels in the second half of this year."

The product is expected to arrive in data centers and other cloud computing applications first, and migrate to consumers shortly thereafter. JEDEC has made the spec available for purchase.

Amber Neely

Amber Neely

Malcolm Owen

Malcolm Owen

Chip Loder

Chip Loder

William Gallagher

William Gallagher

Christine McKee

Christine McKee

Michael Stroup

Michael Stroup

William Gallagher and Mike Wuerthele

William Gallagher and Mike Wuerthele